三星與臺(tái)積電在芯片代工領(lǐng)域的制程之爭(zhēng)��,在最近幾年再次呈現(xiàn)激烈競(jìng)爭(zhēng)的態(tài)勢(shì)��。據(jù)報(bào)道臺(tái)積電的N3B工藝將在今年8月投產(chǎn)����,N3E將在2023年Q2量產(chǎn)。最近����,三星表示�,其3nm芯片有望在Q2實(shí)現(xiàn)量產(chǎn)����。sxpesmc

三星周四表示,它有望在本季度(即未來(lái)幾周)開(kāi)始使用其3GAE(3nm級(jí)柵極全方位早期)制造工藝大批量生產(chǎn)芯片�����。這一宣布不僅標(biāo)志著業(yè)界首個(gè)3nm級(jí)的制造技術(shù)�,而且也是第一個(gè)使用柵極全包圍場(chǎng)效應(yīng)晶體管(GAAFET)的節(jié)點(diǎn)。sxpesmc

三星通過(guò)世界上首次大規(guī)模的GAA 3nm工藝�,加強(qiáng)其技術(shù)領(lǐng)導(dǎo)地位。 三星代工的3GAE工藝技術(shù)是該公司第一個(gè)使用GAA晶體管的工藝���,三星官方稱之為多橋通道場(chǎng)效應(yīng)晶體管(MBCFETs)�。sxpesmc

三星大約在三年前正式推出了其3GAE和3GAP節(jié)點(diǎn)����。當(dāng)該公司描述其使用3GAE技術(shù)生產(chǎn)256Mb GAAFET SRAM芯片時(shí),它提出了一系列的要求���。三星表示��,該工藝將使性能提高30%��,功耗降低50%�,晶體管密度提高80%。不過(guò)�����,對(duì)三星來(lái)說(shuō)����,性能和功耗的實(shí)際組合將如何發(fā)揮���,還有待觀察�。sxpesmc

sxpesmc

sxpesmc

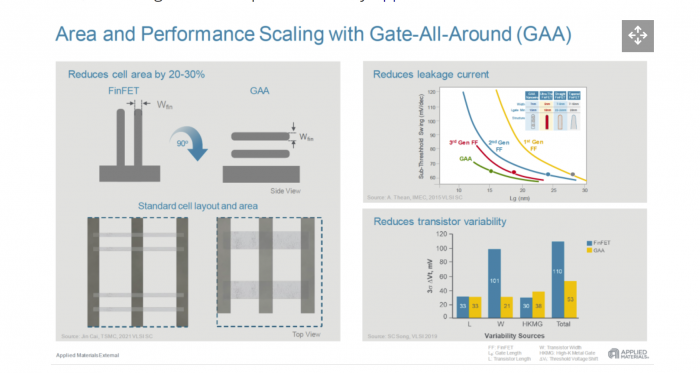

從理論上講����,與目前使用的FinFET相比,GAAFET有許多優(yōu)勢(shì)����。在GAA晶體管中,通道是水平的�����,被柵極所包圍。GAA通道是利用外延和選擇性材料去除形成的��,這使得設(shè)計(jì)者可以通過(guò)調(diào)整晶體管通道的寬度來(lái)精確地調(diào)整它們�。通過(guò)更寬的通道獲得高性能,通過(guò)更窄的通道獲得低功率����。這樣的精度大大降低了晶體管的漏電電流以及晶體管的性能變化,這意味著更快的投產(chǎn)時(shí)間�����、上市時(shí)間和提高產(chǎn)量�。sxpesmc

sxpesmc

sxpesmc

另外,根據(jù)應(yīng)用材料公司最近的一份報(bào)告��,GAAFET有望減少20%-30%的電池面積���。三星的3GAE��,作為一種"早期"的3nm級(jí)制造技術(shù)��,3GAE將主要被三星LSI(三星的芯片開(kāi)發(fā)部門(mén))和兩三個(gè)高級(jí)客戶使用�����??紤]到三星LSI和早期客戶傾向大批量制造芯片,預(yù)計(jì)3GAE技術(shù)將得到相當(dāng)廣泛的使用����,前提是這些產(chǎn)品的產(chǎn)量和性能達(dá)到預(yù)期。sxpesmc

責(zé)編:Editordan

閱讀全文���,請(qǐng)先