近日,瑞薩發(fā)布了符合最新PCIe 6.0規(guī)范的Gen6 Timing時鐘器件��,請看其應用范圍和技術詳情���。7Apesmc

7Apesmc

7Apesmc

應用范圍7Apesmc

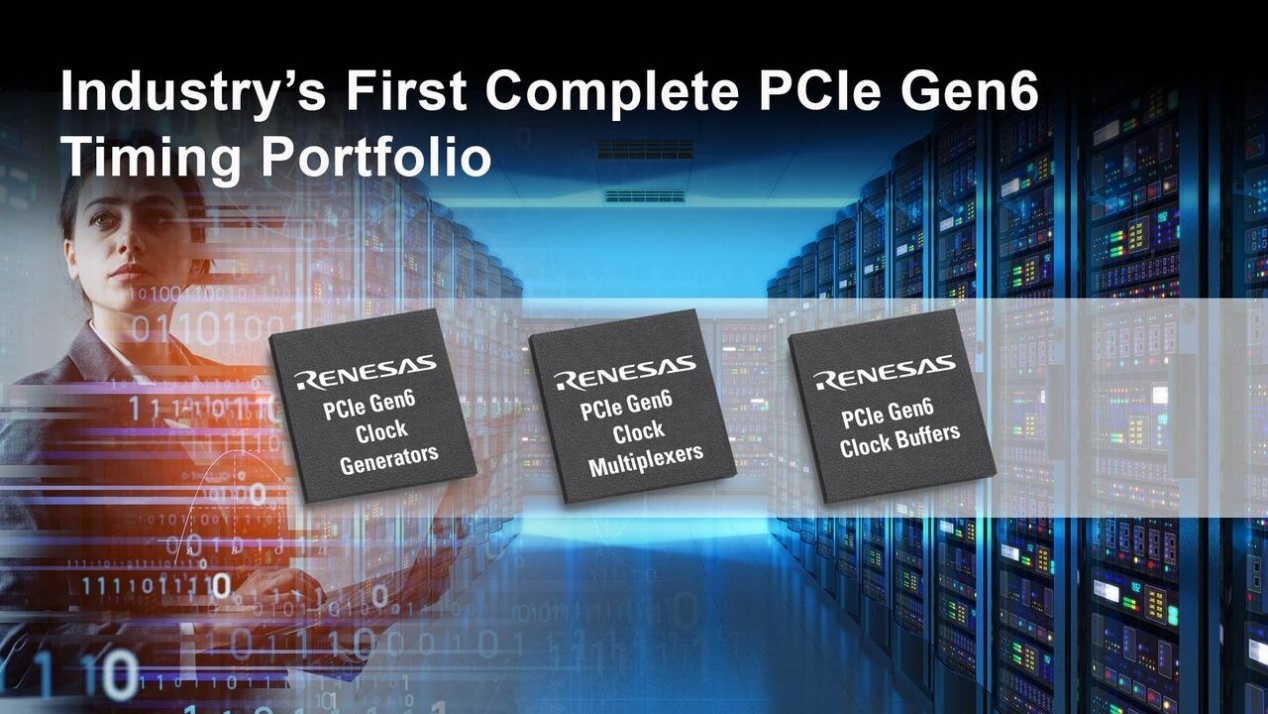

日本瑞薩電子發(fā)布的全球首個PCIe 6.0標準的計時方案�����,包括11款時鐘緩沖器(clock buffer)�����、4款多路復用器(multiplexer)���,以及時鐘發(fā)生器(clock generator)����,為數(shù)據(jù)中心��、云計算�����、網(wǎng)絡����、高速工業(yè)應用提供完整的產(chǎn)品線。7Apesmc

瑞薩電子時鐘產(chǎn)品部副總裁Zaher Baidas表示:“PCIe Gen6時鐘器件將成為數(shù)據(jù)中心�����、高速網(wǎng)絡和其它應用中新設備的核心�。正如我們針對前幾代標準所推出的產(chǎn)品一樣,瑞薩率先為客戶打造了PCIe Gen6時鐘解決方案��,以支持這些新的、更高性能的系統(tǒng)���。同時,瑞薩的客戶也十分了解并信任我們所擁有技術專長和市場洞見��,能夠確保他們的產(chǎn)品滿足未來的需求�。”7Apesmc

Semico Research首席分析師Rich Wawrzyniak表示:“通過為PCIe Gen6提供首個分離時序解決方案,瑞薩使客戶能夠開發(fā)下一代高性能系統(tǒng)�����?��?吹竭@種新功能所帶來的創(chuàng)新很有趣�����,尤其是在考慮新興Chiplet市場的解決方案如何開始發(fā)展時�����,需要提高速度和帶寬作為基本常數(shù)�����。”7Apesmc

技術參數(shù)詳情7Apesmc

1月份��,PCI-SIG組織正式發(fā)布了PCIe 6.0標準規(guī)范���,帶寬繼續(xù)翻倍����,x16單向可達128GB/s�,而且升級了PAM4脈沖調幅信令、FEC前向糾錯機制�、FLIT流量控制單元編碼,是歷代變化最大的一次����。此前,Rambus曾全球首個發(fā)布了完全符合PCIe 6.0的控制器�����,支持全部新特性��。7Apesmc

瑞薩稱���,PCIe 6.0帶寬提升的同時�,要求時鐘抖動(ClockJitter)不超過100fps RMS,而瑞薩的RC190xx系列時鐘緩沖器��、RC192xx系列多路復用器時鐘抖動僅僅4fps RMS��,等于幾乎沒有任何噪聲�����。7Apesmc

同時�,輸入輸出延遲為1.4ns����,輸出輸出偏差為35ps,電源電壓抑制比(PSRR) -80dB@100kHz�����,都可以保證充分的系統(tǒng)穩(wěn)定性�,并支持斷電容忍(PDT)、彈性啟動序列(FSS)�����,以確保一場系統(tǒng)狀態(tài)下的穩(wěn)定性����。7Apesmc

此外�����,功耗也比前代產(chǎn)品降低了30%�����。7Apesmc

瑞薩的PCIe 6.0時鐘緩沖器可選4���、8、13���、16�、20��、24輸出����,多路復用器可選2、4�����、8、16輸出��,封裝尺寸都僅僅3×3毫米����。7Apesmc

責編:EditorTiger